Concordia University

COEN 316

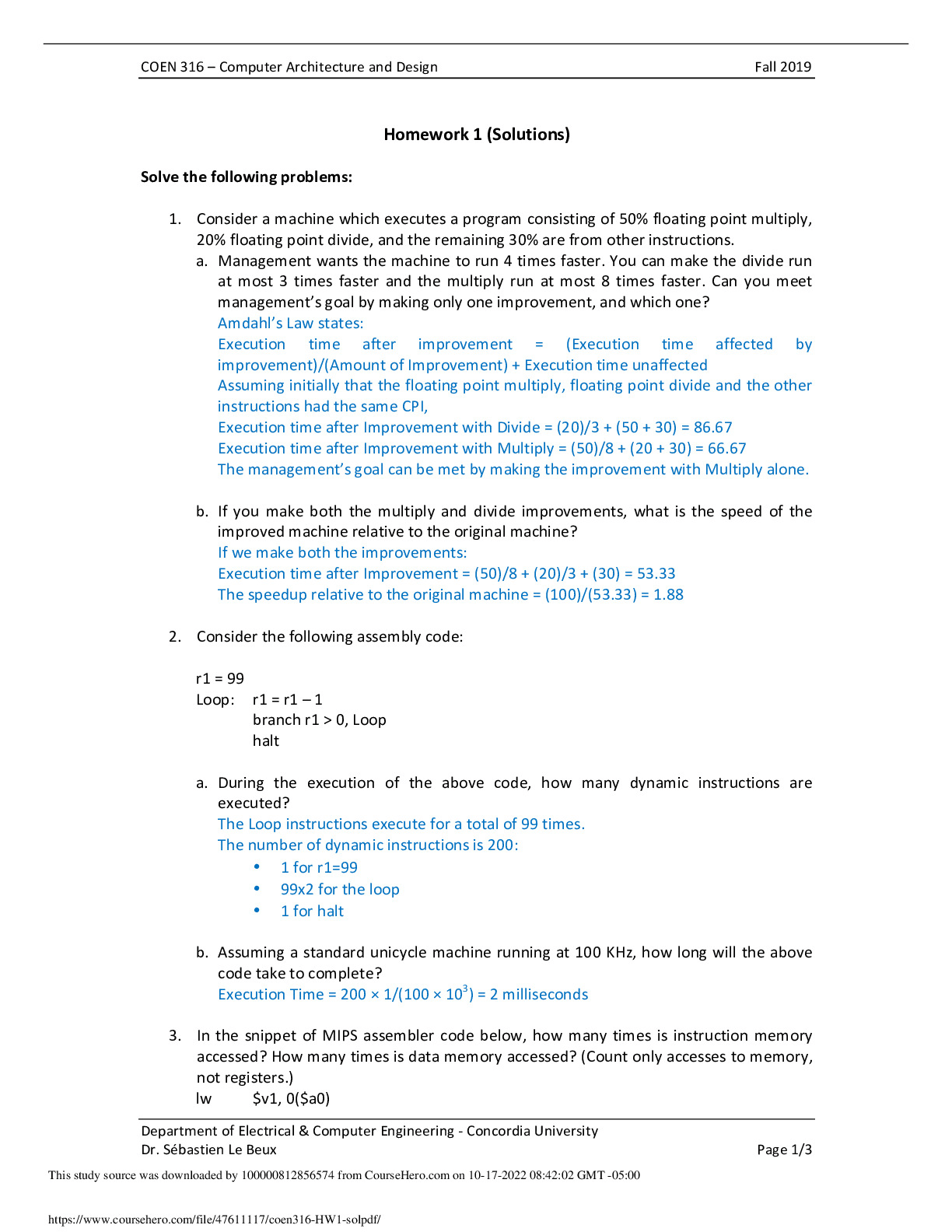

COEN 316 – Computer Architecture and Design Fall 2019

Department of Electrical & Computer Engineering - Concordia University

Dr. Sébastien Le Beux Page 1/3

Homework 1 (Solutions)

Solve the following problems:

1. Consider a machine which executes a program consisting of 50% floating point multiply,

20% floating point divide, and the rem

...[Show More]

COEN 316 – Computer Architecture and Design Fall 2019

Department of Electrical & Computer Engineering - Concordia University

Dr. Sébastien Le Beux Page 1/3

Homework 1 (Solutions)

Solve the following problems:

1. Consider a machine which executes a program consisting of 50% floating point multiply,

20% floating point divide, and the remaining 30% are from other instructions.

a. Management wants the machine to run 4 times faster. You can make the divide run

at most 3 times faster and the multiply run at most 8 times faster. Can you meet

management’s goal by making only one improvement, and which one?

b. If you make both the multiply and divide improvements, what is the speed of the

improved machine relative to the original machine?

2. Consider the following assembly code:

r1 = 99

Loop: r1 = r1 – 1

branch r1 > 0, Loop

halt

a. During the execution of the above code, how many dynamic instructions are

executed?

b. Assuming a standard unicycle machine running at 100 KHz, how long will the above

code take to complete?

3. In the snippet of MIPS assembler code below, how many times is instruction memory

accessed? How many times is data memory accessed? (Count only accesses to memory,

not registers.)

lw $v1, 0($a0)

COEN 316 – Computer Architecture and Design Fall 2019

Department of Electrical & Computer Engineering - Concordia University

Dr. Sébastien Le Beux Page 2/3

addi $v0, $v0, 1

sw $v1, 0($a1)

addi $a0, $a0, 1

4. Suppose that a new MIPS instruction, called bcp, was designed to copy a block of words

from one address to another. Assume that this instruction requires that the starting

address of the source block be in register $t1 and that the destination address be in $t2.

The instruction also requires that the number of words to copy be in $t3 (which is > 0).

Furthermore, assume that the values of these registers as well as register $t4 can be

destroyed in executing this instruction (so that the registers can be used as temporaries

to execute the instruction).

a. Write the MIPS assembly code to implement a block copy without this instruction.

b. Write the MIPS assembly code to implement a block copy with this instruction.

c. Estimate the total cycles necessary for each realization to copy 100-words on the

multicycle machine.

[Show Less]