Test Prep > ECE-GY 6473 Midterm exam with solutions- Fall 2020.

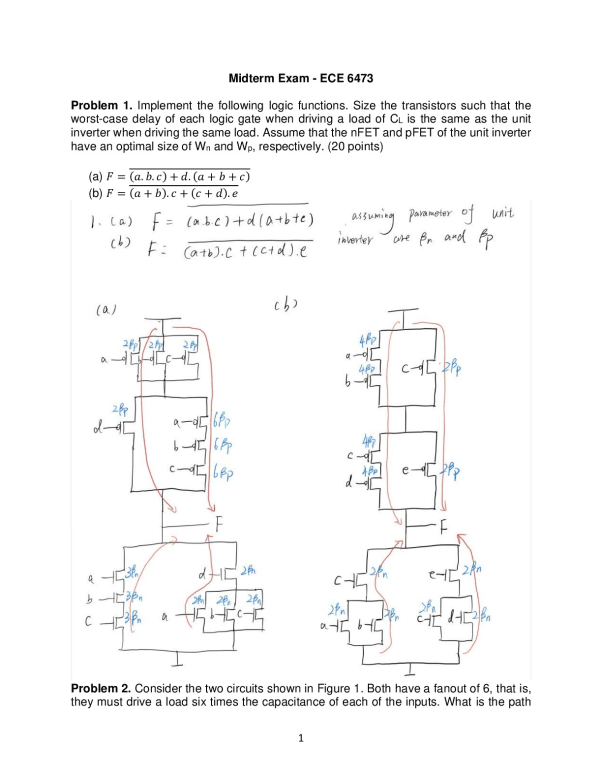

New York University ECE-GY 6473 Midterm exam with solutions- Fall 2020.- Midterm Exam - ECE 6473 Problem 1. Implement the following logic functions. Size the transistors such that Problem 1. Implement the following logic functions. Size the transistors such that the worst-case delay of each logic gate when driving a load of CL is the same as the unit inverter when driving the same load. Ass ...[Show More]

Preview 1 out of 11 pages

Reviews( 0 )

| Category: | Test Prep |

| Number of pages: | 11 |

| Language: | English |

| Last updated: | 1 year ago |

| Downloads: | 0 |

| Views: | 0 |

-preview.png)