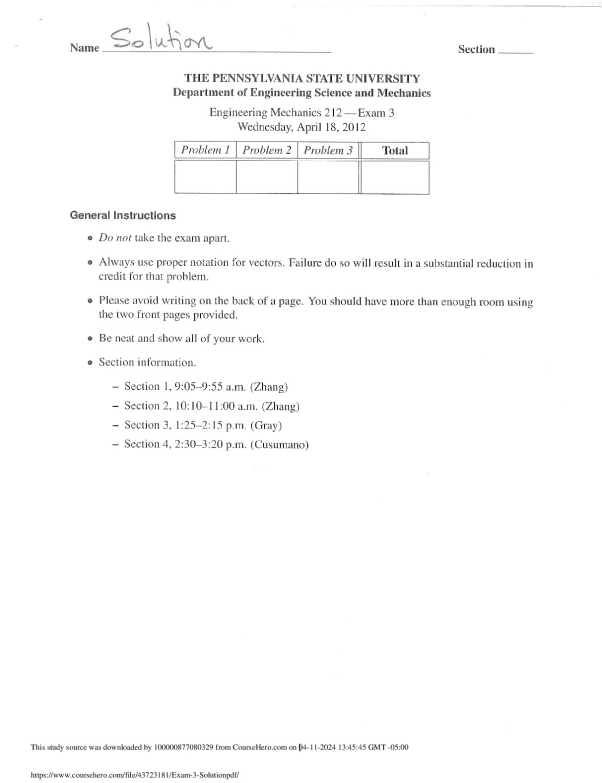

Pennsylvania State University

CMPEN 431

1 (18 pts) Pipelining A company has designed a new 11-stage instruction pipeline processor: IF -> ID -> RF -> E1 -> E2 -> E3 -> E4 -> M1 -> M2 -> M3 -> WB In this architecture, IF is for instruction fetch, ID is for instruction decoding, RF is for register file read, E1 E2, E3 and E4 are for ALU execution, M1, M2 and M3 are for memory

...[Show More]

1 (18 pts) Pipelining A company has designed a new 11-stage instruction pipeline processor: IF -> ID -> RF -> E1 -> E2 -> E3 -> E4 -> M1 -> M2 -> M3 -> WB In this architecture, IF is for instruction fetch, ID is for instruction decoding, RF is for register file read, E1 E2, E3 and E4 are for ALU execution, M1, M2 and M3 are for memory access, and WB is for write back. Assume that the branch target address is calculated at stage E2, and the outcome of the branch condition is determined at stage E4. All ALU instructions go through E1, E2, E3 and E4 stages and similarly all memory (load/store) instructions go through M1, M2 and M3 stages. (a) (3 pts) Explain, considering different execution and resource allocation scenarios, how structural hazards can occur in this 11-stage pipeline? How can structural hazards be eliminated? (b) (3 pts) Explain, giving examples, how data hazards can occur in this pipeline? What are the possible solutions for data hazards (in addition to stalling the pipeline)? (c) (3 pts) How can control hazards happen in this pipeline? Please list three different cases that a control hazard can happen. Illustrate each case clearly. (d) (3 pts) The easiest solution for both data hazards and control hazards is to stall the pipeline. How do you implement such “stalling” in this pipeline? (e) (3 pts) If a stalling policy is used, for this 11-stage pipeline, what is the number of stall cycles for a branch instruction? (f) (3 pts) If you want to implement a branch prediction in this architecture, which pipeline stages need to be modified. Explain why and how. a WB and RI might access the register file at the dome time Mi Muntz and IE might access the memory at same time Fix Reads and writes should happen at different frays of the cycle Eg firsthalf read G second half write

[Show Less]

-preview.png)

-preview.png)

-preview.png)

-preview.png)